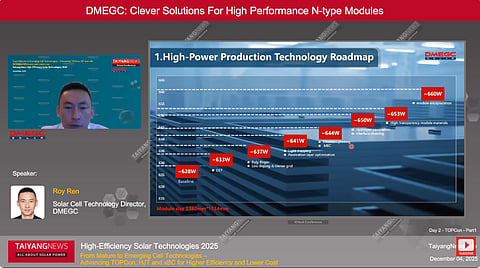

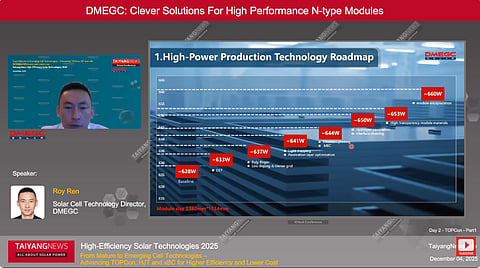

DMEGC presented a roadmap to increase module power from ~628 W to ~660 W through stacked cell and module refinements

Individual cell-level improvements of 0.1%-0.25% efficiency can translate into more than 30 W module-level gains when combined with packaging optimization

BC and TOPCon architectures are expected to evolve in parallel, with 650-670 W modules targeted in the near term, says Ren

As efficiency gains narrow in mature n-type architectures, manufacturers are looking toward process-level optimization. Defect elimination, contact enhancement, hydrogen passivation, and advanced encapsulation are being combined to deliver measurable watt-level improvements.

At the TaiyangNews High-Efficiency Solar Technologies Conference, Roy Ren, Solar Cell Technology Director at DMEGC Solar, presented the company’s roadmap under the title “Clever Solutions for High-Performance n-Type Modules.” The presentation outlined an approach to increasing module output from a baseline of around 628 W to approximately 660 W in a 2,382 mm × 1,134 mm format.

Ren explains how incremental cell- and module-level refinements are stacked to deliver higher output. Starting from a ~628 W baseline, the application of Defect Elimination Technology (DET) increases module power to roughly 633 W. With the addition of poly-finger structures and low doping combined with dense-grid design, output rises further to about 637 W. Subsequent integration of light-trapping, passivation layer optimization, meshless printing, and Metal Enhanced Contact (MEC) pushes the level to around 644 W. Hydrogen passivation and interface cleaning lift the module beyond 650 W. High-transparency module materials add several more watts, and optimized encapsulation techniques bring the total close to 660 W.

DET is designed to mitigate defects introduced during the half-cut process. According to the characterization data presented, EL and IR comparisons between cells with and without DET show measurable gains. The reported efficiency improvement is ~0.25%, mainly reflected in higher open-circuit voltage and fill factor. The approach extends beyond conventional edge passivation by targeting residual recombination sites that remain after cell cutting.

The poly-finger structure focuses on reducing parasitic absorption by selectively removing polysilicon in areas without grid lines. Optical loss analysis indicates that this design can improve efficiency by more than 0.1%, primarily through short-circuit current gains, while slightly affecting fill factor. By lowering optical losses in non-contact regions, the structure enhances current generation without altering the overall architecture.

Low doping, combined with an ultra-dense grid and narrower line width, is another key refinement. By optimizing surface doping to achieve higher sheet resistance and improving current collection through dense metallization patterns, DMEGC reports efficiency gains exceeding 0.1%, with increases in Voc and Isc. This approach balances recombination reduction with resistive loss management.

On the optical side, DMEGC optimizes the SiNx:H anti-reflection layer and introduces multi-layer structures incorporating low-refractive-index films. The data presented indicate an efficiency gain of roughly 0.1%, largely driven by improved Isc. In addition to electrical performance, the multi-layer design enables darker module aesthetics, which are increasingly demanded in certain markets.

Passivation layer optimization focuses on tuning the thickness of the interfacial alumina layer and refining annealing conditions. The presentation shows improvements in Voc and fill factor, translating into efficiency gains above 0.1%. As n-type architectures push toward higher voltages, interface quality becomes increasingly critical.

Metallization improvements include meshless printing and MEC. Meshless printing removes steel mesh wires from the screen-printing area, enabling narrower line widths and improved current transmission. The reported gains exceed 0.1% efficiency, with increases in Voc and Isc. MEC enhances the contact between silver and silicon through localized current injection, reducing passivation damage and improving contact quality. The efficiency gains are again above 0.1%, with improvements mainly in Voc and fill factor.

Hydrogen passivation leverages hydrogen-rich SiNx layers. Under light activation, hydrogen diffuses to passivate defects at the silicon interface. The presentation reports efficiency gains of around 0.15%, primarily reflected in Voc and fill factor. Interface cleaning further improves surface quality through optimized chemical treatment, including NaOH and H₂O₂ adjustments, contributing additional efficiency gains and measurable Voc and Isc improvements. At the module level, high-transparency materials for glass and encapsulants increase light transmission to the cells, adding roughly 2-5 W to module output. Further gains come from overlapped encapsulation, zero-busbar (0BB) encapsulation, and multi-sharding techniques. These packaging strategies reduce inactive areas and increase packing density, contributing more than 8-10 W at the module level.

Ren noted that mainstream BC modules are currently positioned around 650-655 W, with limited 660 W output in production. He also indicated that TOPCon modules are targeting 650-670 W in the coming year. While acknowledging that higher efficiencies bring greater process complexity and cost considerations, he emphasized that BC and TOPCon are expected to continue developing in parallel.

DMEGC’s roadmap lays out how cumulative 0.1%-0.25% cell efficiency improvements can translate into 30 W or more at the module level when integrated with packaging optimization. As competition intensifies beyond the 650 W threshold, such layered and incremental engineering strategies are likely to play a central role in advancing high-performance n-type modules.

To access the full presentation video, titled "Clever Solutions for High-Performance n-Type Modules", click here.